# FET Model Taking Into Account Wave Characteristics of the Active Region and Input Circuits

Vitaly I. Bosy, Yuriy G. Rapoport, and Vasily V. Senchenko

**Abstract**—The new wave model for the field effect transistor (FET) is suggested. Each element of FET layout, including input circuits, is associated with element of equivalent circuit. FET input region includes two parts: variable cross-section microstrip and coplanar lines and a  $T$ -junction. Detailed investigation of the influence of input circuits on FET characteristics has been performed. Approximation of transfer characteristics of input region by these of idealized  $T$ -junction results in substantial distortion of FET transfer coefficient  $|(\mathcal{S}_N)_{21}|$ . Feedback region between gate input line and FET output is responsible for noticeable decrease in maximum available gain (MAG) value for gate width  $W < 60 \mu\text{m}$  and for appearance of gentle maximum in dependence MAG(W) for the  $W/2$  values of about several dozens microns. It has been shown that dependencies of MAG on gate width and frequency change qualitatively when the gate resistance per unit length passes a certain value. This value is estimated. The loads at the ends of gate and drain electrodes can affect resonantly the value of MAG for submicrometer gate FET.

## I. INTRODUCTION

THE theory of distributed transistor has been discussed approximately for about twenty years beginning with the microwave bipolar transistor [1]. This theory develops into three main directions. The first is connected with the investigations of distributed properties of field-effect transistor (FET), as such [2]–[8], including its noise characteristics [3]. The second is motivated by the design of traveling-wave amplifiers [9]–[13] and other devices such as phase shifters, phase modulators and tunable attenuators [14]. The third direction is connected with the development of distributed FET model suitable for the determination of the delay time in high speed integrated circuits [15], [16].

In papers [2]–[9], [12] analytical and numerical models describing some significant properties of distributed FET were developed. It was pointed out in [6], [15], [16] that the wave properties of the electrodes become important for FET's operating at several tens of gigahertz. The existence of optimum value of the gate width  $W_{\text{opt}}$  corresponding to the maximum gain has been proven in papers [6], [8], [9]. It was shown in [8] that the value  $W_{\text{opt}}$  varies in the range of several hundred microns at frequencies below 50 GHz. It was shown that the usual FET structures do not support growing waves [8]. The

Manuscript received October 23, 1994; revised December 14, 1994.

V. I. Bosy and V. V. Senchenko are with the Research Institute Saturn, Kiev 252148, Ukraine.

Y. G. Rapoport is with the T. Shevchenko Kiev University, Physics Department, Astronomy Division, Kiev 25202, Ukraine.

IEEE Log Number 9412035.

methods of balancing of the waves in the gate and drain lines for the design of travelling-wave FET were considered in [10], [12]. Good prospects of the travelling wave transistor were substantiated in [12], [13].

But, in our opinion, some of the other significant features of FET have not been dealt with in most of the modern works.

- 1) The great majority of these works are devoted to the investigation of distributed properties of electrodes of FET and its different modifications. But such properties of input region and their effect on the gain characteristics of FET have not been adequately investigated.

- 2) The effect of feedback region between gate input and FET output on the FET gain is not described.

- 3) The effect of the loads of the coupled line ends was described in paper [17]. But this work was devoted to the supermicrometer gate FET. Such investigation is of interest to submicrometer gate FET design as well.

- 4) The dependence of gain as a function of the gate width for different values of electrode conductivity at the frequency  $F = 1 \text{ GHz}$  was presented in [8] for gate-in drain-out configuration. The possibility of existence of the maxima in dependencies of FET gain on the gate width was shown in papers [6], [8], [9]. But complete investigation of all necessary conditions of the existence of such maxima has not been presented (in particular in our case of gate-in drain-in configuration) and the value of the “critical” gate resistance which determines the character of those dependencies has not been obtained as well.

The investigation of above-mentioned questions of the theory of submicrometer gate FET is the aim of the present work.

## II. MODEL OF THE DISTRIBUTED FET

### A. Equivalent Circuit of the FET on the Basis of the Distributed Transmission Lines on the Active Substrate

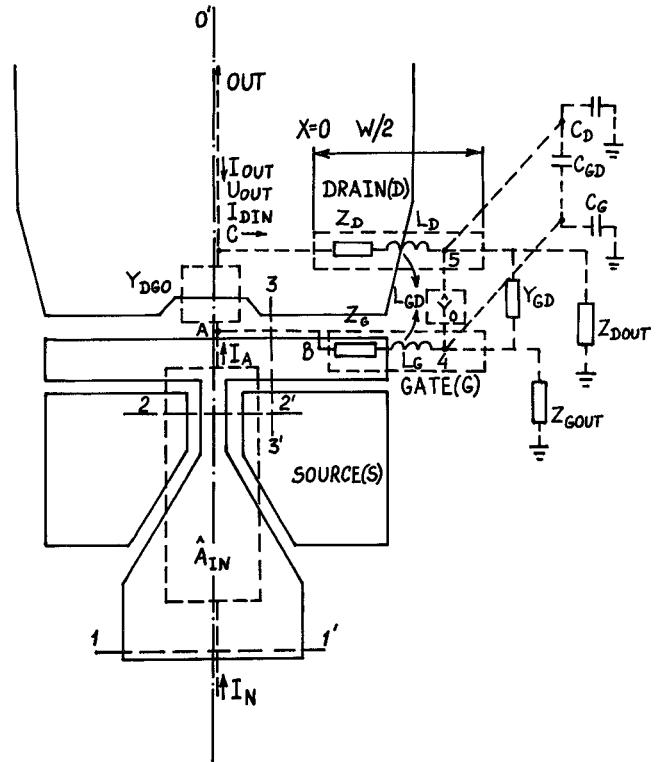

The suggested FET model is based on the equivalent circuit represented in Fig. 1 where the dashed line denotes its correspondence to the FET layout elements. FET is supposed to be symmetrical in relation to the  $OO'$  axis of symmetry. The input region of the FET (region I), which provides the signal transmission from  $11'$  cross-section plane into  $33'$  cross-section, consists of two subregions: variable cross-section microstrip

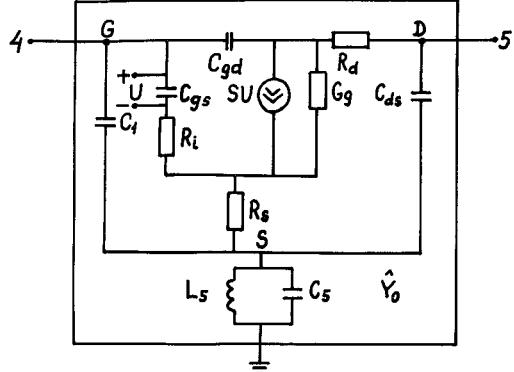

and coplanar lines and a *T*-junction, the interface between them being the 22' cross-section plane. In the equivalent circuit the mentioned region due to the symmetry is represented by the two-port with the transfer matrix  $\hat{A}_{in}$ . The definition of matrix  $\hat{A}_{in}$  is presented in subsection 2.4. The input region parameters are considered to be independent on the FET gate width. The region II, where waves running along the electrodes on the active substrate exist, is modeled by two coupled lines (gate-source and drain-source). The source is assumed to be grounded quite well and the wave effects in it are not taken into account. Both gate and drain lines are supposed to be regular; we neglect the width change of the electrodes along the direction of wave propagation. The inductances and capacitances per unit length  $L_G, L_D, L_{GD}, C_G, C_D, C_{GD}$  describing coupled transmission line effect of the electrode structure are determined analogously to [18]. Complex internal impedances per unit length  $Z_G$  and  $Z_D$  of gate and drain electrodes have been estimated in a similar way to [4]. Fig. 2 presents the equivalent circuit of the two-port describing processes in cross-section plane inside the active substrate of regular gate and drain lines for elementary length  $dx$ . This circuit is similar to those of [19]. But the elements of lumped model [19] describing FET input and output as well as coupled effect of electrode structure are omitted in circuit in Fig. 2. The two-port with the admittance matrix  $\hat{Y}_{DG0}$  describes the feedback region between the input and output of the region II (C and B points respectively). Point B in the equivalent circuit corresponds to the gate input, point C corresponds to the FET output and to the drain input, and the point A corresponds to the *T*-junction center. The points A and B are assumed to be equipotential. The reactivities at the coupled lines ends (edge reactivities) of the regular region II are described by the elements  $Y_{GD}, Z_{Gout}, Z_{Dout}$  of the equivalent circuit.

### B. Telegraph Equations for the Coupled Distributed Transmission Lines on the Active Substrate

The propagation of currents and voltages  $I_G, U_G$  and  $I_D, U_D$  along the gate and drain lines respectively are represented by the set of equations

$$-\frac{\partial \vec{I}}{\partial X} = \hat{Z} \vec{U}, \quad -\frac{\partial \vec{U}}{\partial X} = \hat{Y} \vec{I} \quad (1)$$

where

$$\vec{I} = \begin{vmatrix} I_G \\ I_D \end{vmatrix}, \quad \vec{U} = \begin{vmatrix} U_G \\ U_D \end{vmatrix}$$

$X$  is the direction along the electrodes

$$\begin{aligned} Y_{11} &= Y_{11}^{(0)} + j\omega C_{GD} + j\omega C_G, & Y_{12} &= Y_{12}^{(0)} - j\omega C_{GD} \\ Y_{21} &= Y_{21}^{(0)} - j\omega C_{GD}, & Y_{22} &= Y_{22}^{(0)} + j\omega C_{GD} + j\omega C_D \end{aligned}$$

$\hat{Y}^{(0)}$  is  $Y$ -matrix of the two-port in Fig. 2. [18],  $\hat{Z}$  is the matrix of impedances per unit length

$$Z_{11} = Z_G + j\omega L_G, \quad Z_{12} = Z_{21} = j\omega L_{GD},$$

$$Z_{22} = Z_D + j\omega L_D$$

$\omega = 2\pi F$ ,  $F$  is the operating frequency and the dependence on time  $e^{j\omega t}$  is accepted.

Fig. 1. Problem geometry and FET equivalent circuit taking into account its wave characteristics.

Fig. 2. The FET equivalent circuit in the cross-section.

### C. Calculation of the Transfer Matrix of the Distributed FET

The solution of the system of (1) is

$$\begin{vmatrix} I_G(X) \\ I_D(X) \\ U_G(X) \\ U_D(X) \end{vmatrix} = D_1 \vec{T}_{1+} e^{-jk_1 X} + D_2 \vec{T}_{2+} e^{-jk_2 X} + E_1 \vec{T}_{1-} e^{jk_1 X} + E_2 \vec{T}_{2-} e^{jk_2 X} \quad (2)$$

where

$$\begin{aligned} K_{1,2}^2 &= (\frac{1}{2}) \{ -(F_{11} + F_{22}) \pm [(F_{11} - F_{22})^2 + 4F_{12}F_{21}]^{1/2} \}, \\ F_{11} &= Z_{11}Y_{11} + Z_{12}Y_{21}, \quad F_{12} = Z_{11}Y_{12} + Z_{12}Y_{22} \\ F_{21} &= Z_{21}Y_{11} + Z_{22}Y_{21}, \quad F_{22} = Z_{21}Y_{12} + Z_{22}Y_{22} \end{aligned} \quad (3)$$

The eigenvectors are

$$\vec{T}_{1+} = \begin{vmatrix} N_{1G} \\ N_{1D} \\ D_{1G} \\ 1 \end{vmatrix}, \quad \vec{T}_{2+} = \begin{vmatrix} N_{2G} \\ N_{2D} \\ D_{2G} \\ 1 \end{vmatrix}, \quad \vec{T}_{1-} = \begin{vmatrix} -N_{1G} \\ -N_{1D} \\ D_{1G} \\ 1 \end{vmatrix},$$

$$\vec{T}_{2-} = \begin{vmatrix} -N_{2G} \\ -N_{2D} \\ D_{2G} \\ 1 \end{vmatrix}$$

where

$$\begin{aligned} D_{1G} &= -(K_1^2 + F_{22})/F_{21}, \\ N_{1G} &= jK_1(Z_{22}D_{1G} - Z_{12})/\det Z, \\ N_{1D} &= jK_1(Z_{11} - Z_{21}D_{1G})/\det Z, \\ N_{2G} &= jK_2(Z_{22}D_{2G} - Z_{12})/\det Z, \\ N_{2D} &= jK_2(Z_{11} - Z_{21}D_{2G})/\det Z, \\ D_{2G} &= -(K_2^2 + F_{22})/F_{21} \\ \det Z &= Z_{11}Z_{22} - Z_{21}Z_{12}. \end{aligned}$$

To determine the constants  $D_{1,2}$  and  $E_{1,2}$  it is necessary to use the boundary conditions of continuity of the currents and voltages at inputs and outputs of the gate and drain electrodes. For the circuit in Fig. 1 these conditions have the following form (for FET symmetrical as regards to the line OO')

$$\left(\frac{1}{2}\right)I_A = I_{Gin} + \left[\left(\frac{1}{2}\right)(Y_{DGO})_{11}U_{Gin} + \left(\frac{1}{2}\right)(Y_{DGO})_{12}U_{Din}\right] \quad (4)$$

$$U_A = U_B = U_{Gin}, \quad (5)$$

$$\begin{aligned} U_{Gout}(1 + Z_{Gout}Y_{GD}) - U_{Gout}Z_{Gout}Y_{GD} \\ - I_{Gout}Z_{Gout} = 0, \end{aligned} \quad (6)$$

$$\begin{aligned} U_{Dout}(1 + Z_{Dout}Y_{GD}) - U_{Dout}Z_{Dout}Y_{GD} \\ - I_{Dout}Z_{Dout} = 0 \end{aligned} \quad (7)$$

where

$$I_{(G,D)in} \equiv I_{G,D}(0), I_{(G,D)out} \equiv I_{G,D}(W/2), \quad (8)$$

$$U_{(G,D)in} \equiv U_{G,D}(0), U_{(G,D)out} \equiv U_{G,D}(W/2). \quad (9)$$

$U_A \equiv U_B$  and  $I_A$  are the values of voltage and current at the output of the two-port describing the input region of the FET (region I). Output voltage and current of FET are

$$\begin{aligned} U_{out} &= U_{Din}, \\ I_{out} &= I_{Din} + (Y_{DGO})_{21}U_{Gin} + (Y_{DGO})_{22}U_{Din}. \end{aligned} \quad (10)$$

Solving (2)–(9) and taking into account (10) we obtain the transfer matrix  $\hat{A}_T$  of the region II

$$\begin{vmatrix} -I_{out} \\ U_{out} \end{vmatrix} = \hat{A}_T \cdot \begin{vmatrix} I_A \\ U_A \end{vmatrix}$$

From here it is easy to determine the transfer matrix for the whole FET

$$\hat{A} = \hat{A}_{in} \cdot \hat{A}_T.$$

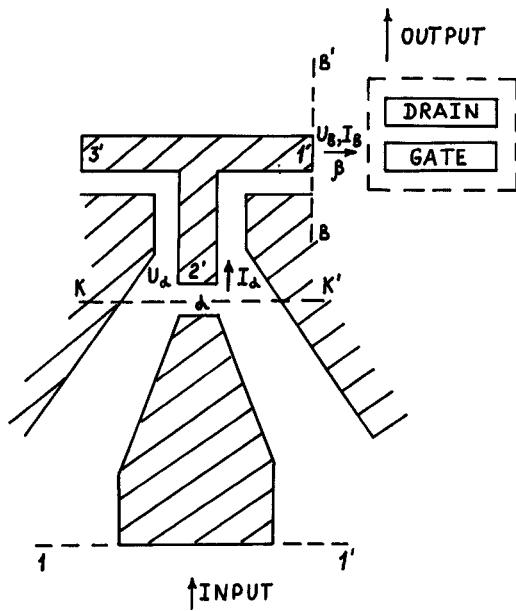

Fig. 3. Calculation of the transfer matrix of input region of the FET.

#### D. Calculation of the Transfer Matrix of Input Region of the FET

The algorithm for the calculation of  $A$ -matrix of the input region is built as follows. The transfer matrix  $\hat{A}_K$  of the subregion consisting of the input microstrip and coplanar line with a variable cross-section (from 1-1' cross section plane to the  $K-K'$  cross section in Fig. 3) is determined similarly to [19]. The outputs of the  $T$ -junction are identified by the primed numbers 1', 2', 3'. Outputs 1' and 2' at the same time are also given by  $\alpha$  and  $\beta$ :  $\alpha \equiv 2'$ ,  $\beta \equiv 1'$ . For symmetrical  $T$ -junction with the symmetrical loads at the side ports it is possible to obtain

$$\begin{vmatrix} U_{\alpha R} \\ U_{\beta R} \end{vmatrix} = \begin{vmatrix} S_{\alpha\alpha}^{(1)} & S_{\alpha\beta}^{(1)} \\ S_{\beta\alpha}^{(1)} & S_{\beta\beta}^{(1)} \end{vmatrix} \cdot \begin{vmatrix} U_{\alpha i} \\ U_{\beta i} \end{vmatrix}$$

where  $U_{K'R}, U_{K'i}$  ( $K = 1', 2', 3'$ ) are the amplitudes of the reflected and incident waves at the port  $K'$  of the  $T$ -junction, respectively,  $U_{1'i} = U_{3'i}$ ,  $U_{1'R} = U_{3'R}$ ,  $\hat{S}$  is the  $S$ -matrix of  $T$ -junction,  $S_{\alpha\alpha}^{(1)} \equiv S'_{2'2}$ ;  $S_{\alpha\beta}^{(1)} \equiv 2S'_{1'2'}$ ;  $S_{\beta\alpha}^{(1)} \equiv S'_{1'2'}$ ;  $S_{\beta\beta}^{(1)} \equiv S'_{11'} + S'_{1'2'}$ .

The matrix  $\hat{S}^{(1)}$  does not possess all the properties of  $\hat{S}$ -matrix, for instance it can't provide the energy conservation in the common form  $|S_{\alpha\alpha}^{(1)}|^2 + |S_{\beta\alpha}^{(1)}|^2 = 1$  (it is necessary to add here the contribution of port 3'). But it is possible to obtain

$$\begin{vmatrix} U_B \\ I_B \end{vmatrix} = \hat{A}^{(1)} \begin{vmatrix} U_\alpha \\ I_\alpha \end{vmatrix}$$

where the matrices  $\hat{A}^{(1)}$  and  $\hat{S}^{(1)}$  are linked by standard transformation. The complete transfer matrix of the input region is

$$\hat{A}_{in} = \hat{A}^{(1)} \cdot \hat{A}_K.$$

To determine the complete  $Y$ -matrix of the FET it is necessary to double the second line (corresponding to the output current of the FET) in the  $Y$ -matrix obtained in the standard way from the  $A$ -matrix  $\hat{A}_{in}$ .

### III. THE TEST CALCULATIONS

With the aim of proof of the validity of designed model the test calculations and comparison of the results obtained by means of present model with independent results obtained by other authors have been done.

#### A. Test Calculations for Equivalent Circuit

1) Analytical expressions for the elements of  $Y$ -matrix for the cross-section of active region of FET (Fig. 2) have been obtained. These expressions have been checked by means of comparison with the expressions for  $Y$ -matrices for simple circuits which are the special cases of circuit in Fig. 2 (for instance, for the case  $C_1 = C_5 = \infty, L_5 = 0$ ) and have been obtained independently. Another test was comparison of the results of calculations by means of our analytical expressions for elements of  $Y$ -matrix of circuit in Fig. 2 with those obtained numerically by means of special software.

2) The test for determination of the characteristics of coupled lines (drain and gate) included independent calculations of the values  $\Delta I_D^{(1)} = I_D(W/2) - I_D(0)$  and

$$\begin{aligned}\Delta I_D^{(2)} &= \int_0^{W/2} dI_D(X) \\ &= \int_0^{W/2} [Y_{21}U_G(X) + Y_{22}U_D(X)] dx.\end{aligned}$$

The difference of this two values was found to be less than 0.5%.

#### B. Comparison of Calculations on the Base of Present Model with Independent Results of Other Authors

1) It has been shown that in the case of little width of the gate ( $W < 20 \mu\text{m}$ ) results of the calculation of MAG agree with accuracy of 2% with those obtained by means of the lumped model [19]. This lumped model [16], [19] as well as sectionized model on its base [20] was compared with experiment [19]–[21] and with results of other works [20]. Particularly, current-voltage characteristics [21],  $S$ -parameters [20] and noise temperature [19] (which is not a subject of present work) have been compared. The difference between theoretical results and experiment was found to be less than 15%.

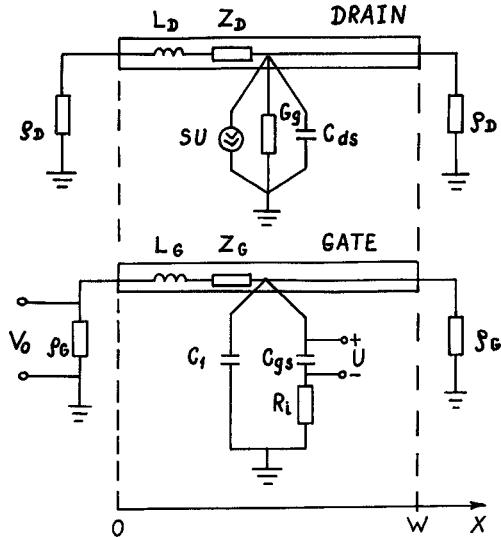

2) We apply our approach to a case considered earlier [9].

Two coupled lines on the active substrate are shown in Fig. 4. In this case the equivalent circuit includes the elements shown in Fig. 4 only. In the model of work [9] these two lines have no direct electromagnetic coupling. But processes in semiconductor determine the “active” coupling between them. The active coupling is represented by current generator in the drain line which depends on the voltage  $U$  on the element  $C_{gs}$  in the gate line. In this case the  $Y$ -matrix  $\hat{Y}^{(0)}$  has the form

$$\begin{aligned}Y_{11}^{(0)} &= Y_{11} = (1/Z_{c1}) + (1/Z_{igs}), \quad Y_{12}^{(0)} = Y_{12} = 0, \\ Y_{21}^{(0)} &= Y_{21} = SK, \quad Y_{22}^{(0)} = Y_{22} = (1/Z_{cds}) + G_g\end{aligned}$$

where

$$\begin{aligned}Z_{c1} &= 1/(j\omega C_1), \quad Z_{igs} = R_i + 1/(j\omega C_{gs}), \\ K &= (1/j\omega C_{gs})/Z_{igs}, \quad Z_{cds} = 1/(j\omega C_{ds})\end{aligned}$$

Fig. 4. Equivalent circuit for lines on the active substrate without direct electrical coupling.

and the wave numbers  $K_1, K_2$  are such as in the case of absence of any connection between lines

$$\begin{aligned}K_1 &= \sqrt{-F_{11}} = \sqrt{-Z_{11}Y_{11}^{(0)}}, \\ K_2 &= \sqrt{-F_{22}} = \sqrt{-Z_{22}Y_{22}^{(0)}}.\end{aligned}$$

We suppose that the values of elements  $\rho_D, \rho_G$  in Fig. 4 provide the absence of reflection of waves at the ends of electrodes

$$\rho_D = \sqrt{Z_{22}/Y_{22}}, \quad \rho_G = \sqrt{Z_{11}/Y_{11}}.$$

This coefficient of the voltage transmission  $K_U = U_{D\text{out}}/U_{G\text{in}} \equiv U_D(W)/U_G(0)$  was determined analytically in the papers [9], [10]

$$K_U = \frac{SK\rho_D}{2j(K_1 - K_2)}(e^{-jK_1 W/2} - e^{-jK_2 W/2}). \quad (11)$$

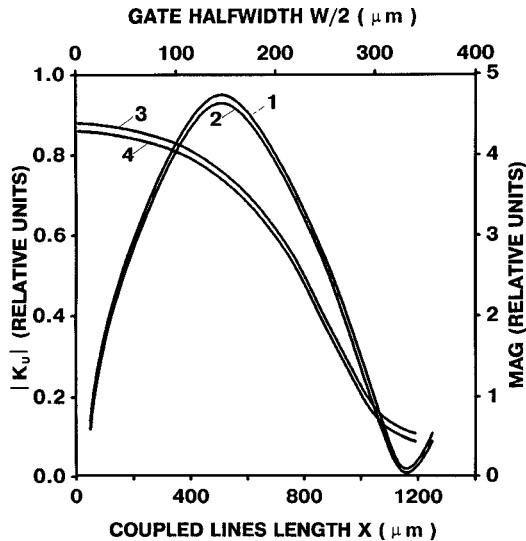

The values  $|K_U|$ , determined by means of the procedure developed in present work and from the (5) are presented in Fig. 5 (curves 1 and 2 respectively). It is seen that the results of numerical and analytical calculations coincide with the graphic accuracy.

3) The work [5] developed the model of the distributed FET with equipotential drain ( $Z_D = 0$  and  $L_D = 0$ ),  $L_{GD} = 0$ ,  $Z_{G\text{out}} = Z_{D\text{out}} = \infty$ . Variation MAG( $W/2$ ) obtained by means of such model is presented by the curve 3 at Fig. 5. Curve 4 in this figure corresponds to the calculation by means of method of present work with  $L_{GD} = L_D = 0$ ,  $Z_D = 10^{-3}\Omega$ ,  $Z_{G\text{out}} = Z_{D\text{out}} = 10^8\Omega$ . The results of two independent methods in this case coincides with the graphic accuracy as well.

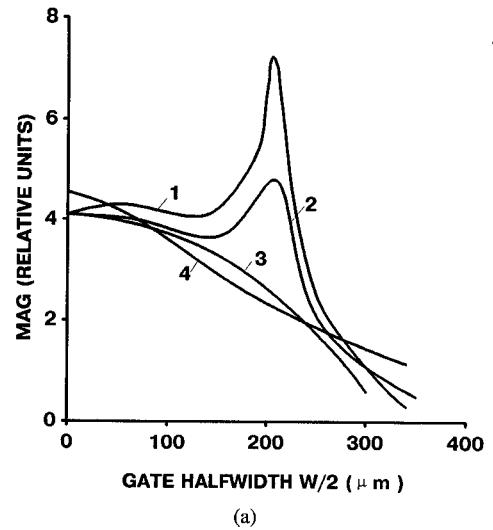

4) The curve 4 in Fig. 6(a) was plotted for frequency  $F = 40$  GHz and parameters of electromagnetic coupling between the electrodes  $L_G, L_D, L_{GD}, C_G, C_D, C_{GD}$  and impedances  $Z_G, Z_D$  taken from [4] (in particular  $R_g = \text{Re}(Z_G) = 0.055 \Omega/\mu\text{m}$ ). This curve behaves qualitatively such as proper curve (for  $F = 40$  GHz) from [4] (with no peak, see Fig. 5 in [4]).

Fig. 5. Dependencies of the absolute value of voltage transmission coefficient  $|K_U|$  on the coupled lines length ( $X$ ) in the absence of the direct electrical coupling (curves 1, 2) and of the MAG on gate halfwidth ( $W/2$ ) of FET with equipotential drain (curves 3, 4). Curves 1, 4—results of the calculations by means of method developed in present work; 2—analytic calculation by means of method [8]; 3—calculation by means of method [9].

Numerical difference between these curves is connected with the difference in the equivalent circuit elements for the FET cross-section in this work and in work [4] (the values of these elements had not been presented in [4]).

#### IV. RESULTS OF THE NUMERICAL CALCULATIONS

We should note that all results are presented for the case when input circuits of FET are lossless (two-port with the transfer matrix  $\hat{A}_{in}$  in Fig. 1 is purely reactive and any lumped active resistance is absent).

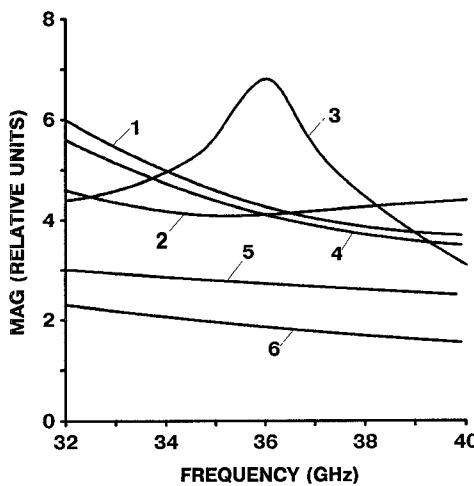

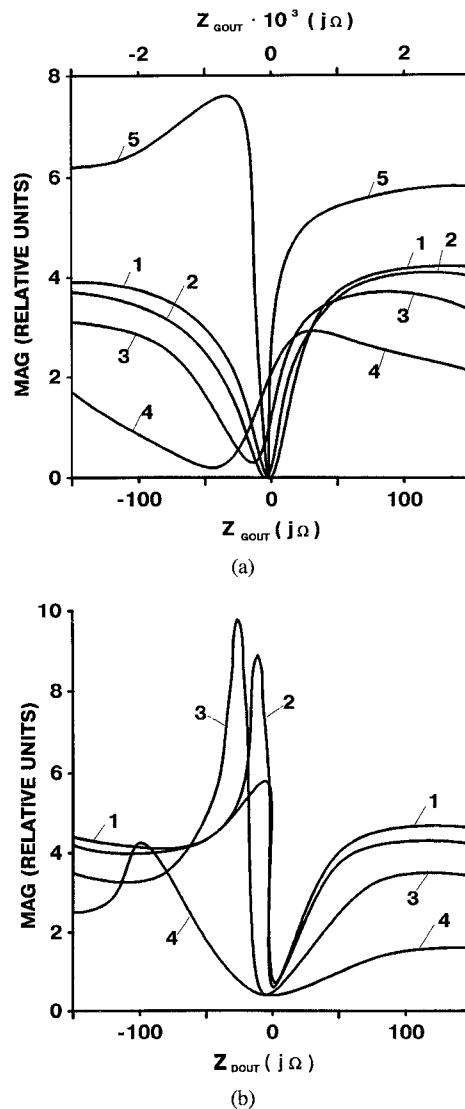

As it is seen from Fig. 6(a) (curves 1–4) there is a critical value of  $R_{g0}$  for the gate resistance per unit length  $R_g = \text{Re}(Z_G)$ , such that when  $R_g < R_{g0}$ , the function MAG ( $W$ ) has the maximum (at  $W/2 \approx 200 \mu\text{m}$  for the considered FET), and when  $R_g > R_{g0}$  such maximum is absent. When  $F = 36 \text{ GHz}$ , (curves 1–3 in Fig. 6(a) and curves 1–3 in Fig. 6(b)) the value of  $R_{g0}$  is between  $0.021 \Omega/\mu\text{m}$  and  $0.028 \Omega/\mu\text{m}$ . The comparison of curves 1 in Fig. 6(a) (the admittance matrix of the feedback region  $\hat{Y}_{DG0} = \hat{0}$ ) and 1 in Fig. 6(b) ( $\hat{Y}_{DG0} \neq \hat{0}$ ) demonstrates the role of the cut in the drain electrode (see Fig. 1), which decreases the feedback between output of the FET and input of the gate, in the improvement of the gain properties of FET. If one takes into account the non-zero admittance matrix  $\hat{Y}_{DG0}$  of the feedback region (which is supposed to be on the passive substrate), for  $W/2$  equal to several dozens of microns there appears an additional gentle maximum in the dependence MAG ( $W$ ) (curve 1 in Fig. 6(b)). It should be noted that when the inductance “gate-drain” is not taken into account ( $L_{GD} = 0$ ), there is no maximum of MAG at  $W/2 = 200 \mu\text{m}$  even if  $R_g < R_{g0}$  (curve 2 in Fig. 6(b)) as well as for the case of equipotential drain (curves 3, 4 in Fig. 5). The dependence MAG( $W'/2$ ), when  $W'$  changes in wide ranges and  $R_g = 0.01460 \Omega/\mu\text{m} \ll R_{g0}$ , is represented by the curve 3 (the corresponding values of  $W'/2$  are shown

(a)

(b)

Fig. 6. Variation of the gain factor MAG with the FET gate halfwidth.  $F = 36 \text{ GHz}$  (with exception of curve 4 in (a));  $L = 0.23 \text{ pH/mm}$  (with exception of curves 4 in (a) and (b)). (a)  $\hat{Y}_{DG0} = \hat{0}$ ; 1— $R_g = 0.014 \Omega/\mu\text{m}$ ; 2— $0.021 \mu\text{m}$ ; 3— $0.028 \Omega/\mu\text{m}$ ; 4— $0.055 \Omega/\mu\text{m}$  (for this curve  $F = 40 \text{ GHz}$ ). (b) 1, 2— $\hat{Y}_{DG0} \neq \hat{0}$ ; 3— $\hat{Y}_{DG0} = \hat{0}$ ; 1— $R_g = 0.014 \Omega/\mu\text{m}$ ; 2— $0.014 \Omega/\mu\text{m}$ ; 3— $0.014 \Omega/\mu\text{m}$  (for this dashed curve the values  $W'/2$  of the gate halfwidth are shown on the upper horizontal axis).

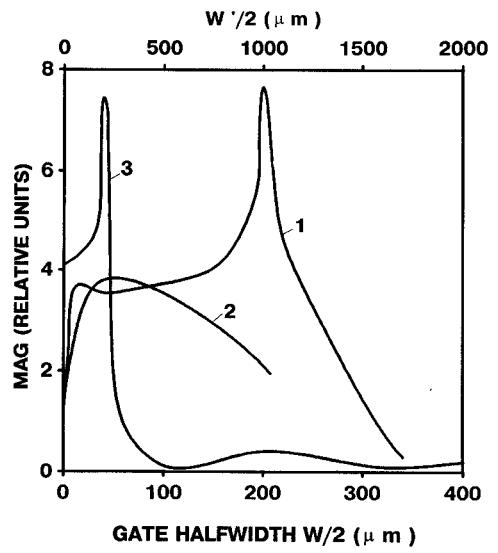

on the upper horizontal axis in Fig. 6(b)). The smaller of two wavelengths propagating in coupled lines,  $\lambda_1$ , approximately equals  $800 \mu\text{m}$  ( $F = 36 \text{ GHz}$ ) and is close to the “period” of this dependence (about  $1000 \mu\text{m}$ ) at a given  $R_g < R_{g0}$ . The optimal value  $W/2 = W_0/2$ , at which the maximum value of MAG is achieved, equals about  $200 \mu\text{m}$ , that is, in this case  $W_0/2 \approx \lambda_1/4$ . The frequency dependencies of MAG for different values of  $W/2$ , shown in Fig. 7, have different forms for  $R_g < R_{g0}$  (curves 1–3) and  $R_g > R_{g0}$  (curves 4–6) as well. In the former case there is an optimum value of the  $W/2$  when the minimum variation of the MAG value in the bandwidth is reached (curve 2), and also, (another) optimum value of  $W/2$ , when the maximum of MAG at some frequency inside the frequency range takes place (curve 3). Naturally, the maximum MAG( $F$ ) for  $W/2 = 205 \mu\text{m}$

Fig. 7. Variation of the gain factor MAG with the frequency  $F$  ( $\hat{Y}_{DG0} = 0$ ). Curves 1-3 are plotted for  $R_g = 0.014 \Omega/\mu\text{m} < R_{g0}$ , curves 4-6 are for  $R_g = 0.044 \Omega/\mu\text{m} > R_{g0}$ . 1, 4 —  $W/2 = 35 \mu\text{m}$ ; 2, 5 —  $154 \mu\text{m}$ ; 3, 6 —  $205 \mu\text{m}$ .

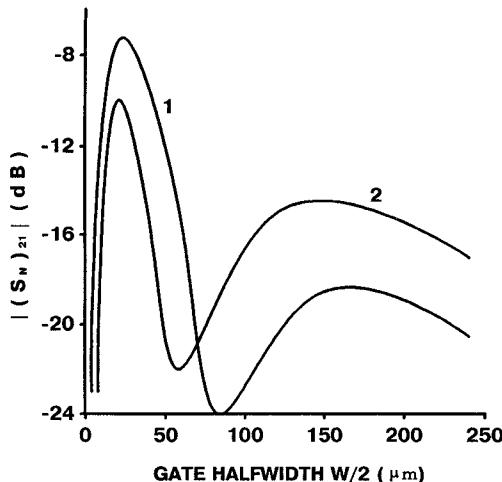

(curve 3) is reached at the  $F = 36$  GHz (see also curve 1, Fig. 6(a)). Dependencies of MAG on loads at the end of the gate and drain electrodes are shown in Fig. 8(a) and (b), respectively, for  $F = 36$  GHz and  $R_g = 0.042 \Omega/\mu\text{m} > R_{g0}$  with the exception of curve 5 in Fig. 8(a) for which  $R_g = 0.014 \Omega/\mu\text{m} < R_{g0}$ . For our estimations for our FET,  $Z_{G\text{out}} \simeq Z_{G\text{out}}^{(0)} \simeq -j8.84 \cdot 10^3 \Omega$ ,  $Z_{D\text{out}} \simeq Z_{D\text{out}}^{(0)} \simeq -j4.92 \cdot 10^2 \Omega$  (at frequency  $F = 36$  GHz). Dependencies MAG ( $Z_{G\text{out}}$ ) have minima at values of modulus of  $Z_{G\text{out}}$  less than several dozens of Ohms (curves 1-4, Fig. 8(a)). For  $W/2 \sim (100 \div 200) \mu\text{m}$  these dependencies have very smooth maxima for the values of inductive loads of about  $Z_{G\text{out}} \sim j(100 \div 50) \Omega$ . Minima of MAG ( $Z_{D\text{out}}$ ) for  $W/2 \leq 200 \mu\text{m}$  take place for capacitive loads with absolute value  $|Z_{D\text{out}}|$  less than  $12 \Omega$  (curves 1-4, Fig. 8(a)). Their maxima take place at  $Z_{D\text{out}} \simeq -j30 \Omega$  for  $W/2 = 100$  and at  $Z_{D\text{out}} \simeq -j170 \Omega$  for  $W/2 = 200$  (curves 4 and 1 in Fig. 8(b) respectively). For  $R_g < R_{g0}$  MAG ( $Z_{G\text{out}}$ ) and MAG ( $Z_{D\text{out}}$ ) do not change qualitatively in comparison with the case of  $R_g > R_{g0}$  (Fig. 8) with the exception of appearance of the maximum in the dependence of MAG ( $Z_{G\text{out}}$ ) at  $Z_{G\text{out}} \simeq -j1.6 \cdot 10^3 \Omega$  (curve 5, Fig. 8(a)). It is interesting to note, that for  $W/2 = 200 \mu\text{m}$   $R_g \cong 0.014 \Omega/\mu\text{m} < R_{g0}$  and  $Z_{G\text{out}} \cong 8.84 \cdot 10^3 \Omega$  maximum of MAG ( $Z_{D\text{out}}$ ) takes place at  $Z_{D\text{out}} \cong -j440 \Omega$ . This value is very close to the value  $Z_{D\text{out}}^{(0)}$ , which takes place (in our estimation) for our FET at this frequency.

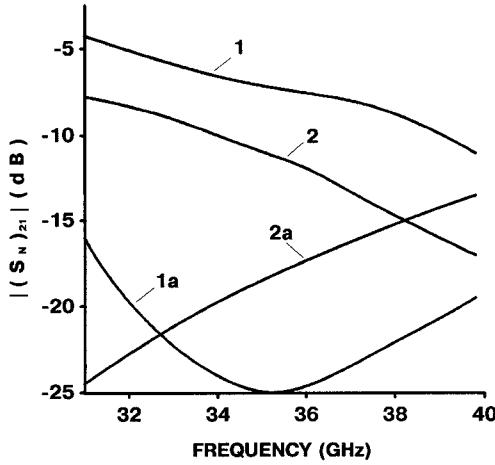

Figs. 9-11 illustrate the effect of input circuits on FET characteristics.

Fig. 9 shows variations of the absolute value  $|(S_N)_{21}|$  of the element of  $S$ -matrix  $S_N$  of whole FET for frequency  $F = 36$  GHz and  $R_g = 0.044 \Omega/\mu\text{m}$  with the FET gate width. Curves 1 and 2 corresponds to the input regions with idealized transfer matrix ( $A_{\text{in}})_{12} = (A_{\text{in}})_{21} = 0$ ,  $(A_{\text{in}})_{11} = 0.5$ ,  $(A_{\text{in}})_{22} = 1$  and with the real one respectively. Ignoring the real transfer matrix of FET input region when the gate width values are within the range  $20 \mu\text{m} \leq W/2 \leq 100 \mu\text{m}$  results in a  $|(S_N)_{21}|$  deviation between (3  $\div$  10) $B$ .

Fig. 8. Variation of the gain factor MAG with the loads at the ends of the (a) gate and (b) drain electrodes;  $R_g = 0.042 \Omega/\mu\text{m} > R_{g0}$  with the exception of curve 5 in (a). 1 —  $W/2 = 35 \mu\text{m}$ ; 2 —  $50 \mu\text{m}$ ; 3 —  $100 \mu\text{m}$ ; 4 —  $200 \mu\text{m}$ . For curve 5 at Fig. 8(a)  $R_g = 0.014 \Omega/\mu\text{m} < R_{g0}$ ,  $W/2 = 200 \mu\text{m}$ , and the values of the loads  $Z_{G\text{out}}$  are shown on the upper horizontal axis.

Fig. 10 shows variations of  $|(S_N)_{21}|$  with frequency  $F$  for gate width values  $W/2 = 36 \mu\text{m}$  (curves 1, 2) and  $92 \mu\text{m}$  (curves 1a, 2a) respectively. Curves 1, 1a correspond to idealized input circuit (with idealized  $A$ -matrix) and curves 2, 2a-to real input circuit.

As it is seen from Figs. 9 and 10, for  $F = 36$  GHz some characteristic value of gate width  $W = W_0$  exists ( $W_0/2 \simeq 75 \mu\text{m}$ ). For  $W < W_0$  and for  $W > W_0$  difference  $\Delta S^{(1,2)} = |(S_N)_{21}|^{(1)} - |(S_N)_{21}|^{(2)}$  has different signs. Superscripts (1) and (2) corresponds to FET's with real and idealized  $A$ -matrix of input circuit respectively. In a similar way, for the value of  $W/2$  large enough some characteristic frequency  $F = F_0$  exists inside frequency range  $F = 31 \div 40$  GHz. (Particularly for  $W/2 = 92 \mu\text{m}$   $F_0 \simeq 33$  GHz). For  $F > F_0$  and  $F < F_0$   $\Delta S^{(1,2)}$  has different signs as well. At the same time, in the region of smaller values of gate width (particularly for  $W/2 = 32 \mu\text{m}$ ) the sign of  $\Delta S^{(1,2)}$  is conserved inside all above-mentioned frequency range. Fig. 11 shows variation of

Fig. 9. Variation of the absolute value of transfer coefficient  $|S_N|_{21}$  (in decibels) with gate halfwidth ( $W/2$ ) for idealized (curve 1) and real (curve 2) transfer matrices  $\hat{A}_{in}$  of the FET input region ( $F = 36$  GHz).

Fig. 10. Variations of transfer coefficient absolute value  $|S_N|_{21}$  with frequency ( $F$ ) for idealized (curves 1, 1a) and real (curves 2, 2a) transfer matrices  $\hat{A}_{in}$  of the FET input region. Curves 1.2— $W/2 = 36$   $\mu\text{m}$ ; curves 1a, 2a— $W/2 = 92$   $\mu\text{m}$ .

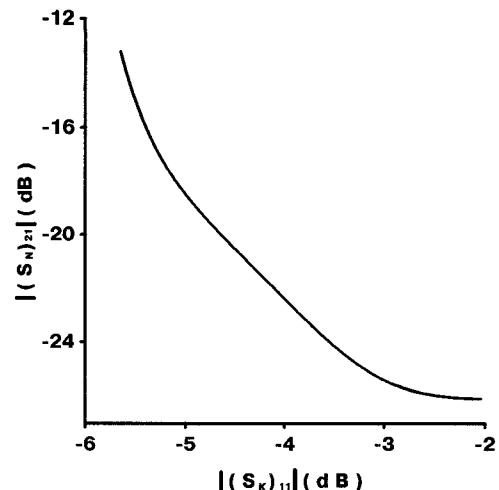

$|S_N|_{21}$  with the absolute value of element  $(S_K)_{11}$  of  $S$ -matrix of part of input region (between cross-sections 11' and  $KK'$  in Fig. 3). With variation of  $|S_K|_{11}$  in the range (-2  $\div$  -5.5) dB the value of  $|S_N|_{21}$  varies in the range (-27  $\div$  -13) dB. Therefore input region affect significantly the transfer characteristics of FET.

## V. CONCLUSION

A new wave model of FET including its input circuits is suggested. Each element of real FET layout is associated with appropriate element of equivalent circuit. Main results obtained by means of this model are the following.

1) Real transfer characteristics of FET input region should be taken into account. Their ignoring results in significant distortion of FET transfer coefficient  $|S_N|_{21}$ . For  $W/2 < 100$   $\mu\text{m}$  this deviation is between (3  $\div$  10) dB. With the variation of absolute value  $|S_K|_{11}$  of the element of  $S$ -matrix of input region part (between cross-sections 11' and

Fig. 11. Variation of transfer coefficient absolute value  $|S_N|_{21}$  with absolute value  $|S_K|_{11}$  of the  $S$ -matrix element of input region part (between cross-sections 11' and  $KK'$  at Fig. 3).

$KK'$  in Fig. 3) in the range (-2  $\div$  -5.5) dB value  $|S_N|_{21}$  varies in the range (-27  $\div$  -13) dB.

2) Taking account the feedback region (between input of the gate and output of FET) leads to noticeable decrease in the value of  $\text{MAG}(W)$  for  $W < 60$   $\mu\text{m}$  and to the appearance of gentle maximum in dependence  $\text{MAG}(W)$  for the  $W/2$  values of about several dozens microns.

3) There is a qualitative difference in variations  $\text{MAG}(W)$  and  $\text{MAG}(F)$  when the real part value of gate impedance per unit length  $R_g$  takes place in different regions:  $R_g < R_{g0}$  and  $R_g > R_{g0}$ . In the first case maxima in the variations  $\text{MAG}(W)$  and  $\text{MAG}(F)$  as well as minimum of the  $\text{MAG}$  non-uniformity within the frequency range exist when values of  $W/2$  are about hundreds microns. When  $F = 36$  GHz the value of  $R_{g0}$  is between 0.021 and 0.028  $\Omega/\mu\text{m}$ . But under zero value of mutual inductance of gate and drain ( $L_{GD} = 0$ ) such maximum is absent even for  $R_g < R_{g0}$ .

4) The loads at the ends of gate and drain ( $Z_{Dout}$ ) electrodes may affect resonantly the  $\text{MAG}$ . For  $W/2 = 200$   $\mu\text{m}$  and  $R_g = 0.014 \Omega/\mu\text{m}$  maximum of  $\text{MAG}(Z_{Dout})$  takes place at  $Z_{Dout} \simeq -j440 \Omega$ . This value is very close to those takes place (in our estimation) for our FET at this frequency.

## REFERENCES

- [1] A. J. Wahl, "Distributed theory for microwave bipolar transistors," *IEEE Trans. Electron Dev.*, vol. ED-21, pp. 40-49, 1974.

- [2] W. Heinrich, "Distributed equivalent-circuit model for travelling-wave FET design," *IEEE Trans. Microwave Theory Tech.*, vol. 35, p. 487, May 1989.

- [3] ———, "High-frequency MESFET noise modeling including distributed effects," *IEEE Trans. Microwave Theory Tech.*, 7. W. Heinrich and H. L. Hartnagel, "Field-theoretic analysis of signal propagation on FET electrodes including losses and small signal amplification," *Int. J. Electron.*, vol. 58, no. 4, pp. 613-627, 1985; vol. 37, pp. 836-842, 1989.

- [4] R. L. Chang, T. J. Shieh, W. A. Davis, and R. L. Carter, "Modelling and analysis of GaAs MESFET's considering the wave propagating effect," in 1989 *IEEE MTT-S Dig.*, L-9, p. 371.

- [5] V. A. Moskaluk, V. I. Timofeyev, and I. A. Shovkin, "Distributed model of the microwave field-effect transistor," *Radioelectron. Commun. Syst.*, translation of *Izvestiya VUZov. Radioelectronika (USSR)*, vol. 30, pp. 32-35, May 1987.

- [6] W. Heinrich, "On the limits of FET modelling by lumped elements" *Electron. Lett.*, vol. 22, no. 12, pp. 630-632, June 1986.

- [7] W. Heinrich and H. L. Hartnagel, "Field-theoretic analysis of signal propagation on FET electrodes including losses and small signal amplification," *Int. J. Electron.*, vol. 58, no. 4, pp. 613-627, 1985.

- [8] —, "Wave propagation on MESFET electrodes and its influence on transistor gain," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-35, pp. 1-8, 1987.

- [9] A. S. Podgorski and L. Y. Wei, "Theory of travelling-wave transistors," *IEEE Trans. Electron Dev.*, vol. ED-26, pp. 1845-1853, Dec. 1982.

- [10] C.-J. Wei, "Novel design of travelling-wave FET," *Electron. Lett.*, vol. 13, pp. 461-463, 1983.

- [11] N. Sebati, P. Gamand, C. Varin, F. Pasqualini, and J.-C. Mennier, "Continuous active T-gate travelling-wave transistor," *Electron. Lett.*, vol. 25, pp. 403-404, 1989.

- [12] A. J. Holden, D. R. Daniel, I. Davies, C. H. Oxley, and H. D. Rees, "Gallium arsenide travelling-wave field-effect transistors," *IEEE Trans. Electron Dev.*, vol. ED-32, pp. 61-66, 1985.

- [13] S. M. El-Gazaly and T. Itoh, "Travelling-wave inverted-gate field-effect transistors: Concept, analysis and potentials," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1027-1032, June 1989.

- [14] K. Frike and H. L. Hartnagel, "GaAs MESFET optimization and new device applications based on wave property studies," in 1985 IEEE MTT-S Dig., pp. 192-195.

- [15] P. H. Lanbrooke, "Some effects of wave propagation in the gate of microwave MESFET," *Electron. Lett.*, vol. 14, pp. 21-22, 1978.

- [16] A. K. Goel and C. R. Westgate, "Modelling of the transverse delay in GaAs MESFET's," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 1411-1417, 1988.

- [17] K. Frike and H. L. Hartnagel, "Experiment study of MESFET travelling-wave structures," *Int. J. Electron.*, vol. 58, no. 4, p. 629, 1985.

- [18] V. M. Krasnoperkin, N. G. Prokofyev, and G. S. Samokhin, "Software for analysis of devices on the base of coupled strip lines," *Electron. Tech.*, series "Microwave electronics," no. 1, p. 66, 1984 (in Russian).

- [19] V. I. Timofeev, "Modelling of the low-noise regime of the submicron FET," *Radioelectron. Commun. Syst.*, translation of *Izvestiya VUZov. Radioelektronika (USSR)*, vol. 36, no. 3-4, pp. 57-63, 1993.

- [20] V. A. Moskaliuk and V. I. Timofeev, "Sectionalized model of the microwave FET taking into account distributed effects," in *Automatic Design in Electronics*, Republic Science-Techniques Collected Volume, issue no. 33. Kiev Ukraine: Techniques Press, 1986, pp. 93-97 (in Russian).

- [21] V. V. Minakov and V. A. Moskaliuk, "Analysis of the model of submicron field-effect transistor from the position of adaptive design," *Radioelectron. Commun. Syst.*, translation of *Izvestiya VUZov. Radioelektronika (USSR)*, vol. 31, no. 6, pp. 64-72, 1988.

**Yuriy G. Rapoport** was born in Kiev, Ukraine, on February 28, 1956. He graduated from Kiev University (Physics faculty, Department of Theoretical Physics), Kiev, Ukraine, in 1978, and received the Ph.D. degree from Kiev University in 1986. His thesis research included theoretical analyses of interaction of magnetostatic and electromagnetic and acoustic waves in layered structures, and was performed under the direction of Prof. N. Ya. Kot-sarenko.

During 1978-1981 he was an Engineer in the Research Institute Saturn, Kiev, Ukraine, a post-graduate student in the Research Institute Orion from 1982-1984, and during 1985-1991 he was a Junior Researcher, Researcher and Senior Researcher in the Research Institute Saturn, where he led an active research effort in microwave field theory, including ferrites and integrated structures. Since the end of 1991 he has been with the Space Research laboratory, Kiev University. His research interests include the theory of magnetostatic waves, methods of numerical modeling of guided wave structures, integrated active devices and nonlinear waves in ferrites, plasma and atmosphere.

Dr. Rapoport is a member of the Ukrainian Physical Society.

**Vasily V. Senchenko** was born on July 26, 1946, in Ukraine. He graduated from the Radiophysics Department of the Kharkov University, Ukraine, and received the speciality of radiophysics and electronics engineer and the Ph.D. degrees in antennas and microwave techniques from the Moscow Electronic Technical Institute in 1969 and 1982, respectively.

From 1969-1983 he worked in the Research Institute Saturn as a Microwave Research Engineer on low noise amplifiers, multipliers, oscillator sources, and various other solidstate devices. During 1984-1994 he was working as a Chief of the Computer Modeling of MMIC's at the Research Institute Saturn. His research interests are in electromagnetic theory and full-wave modelling methods applied microwave integrated circuits. His recent activity include the development of the singular integral equation technique for planar transmission lines.

**Vitaly I. Bosy** graduated from the radioelectronic department of the Kiev Polytechnical Institute and received the speciality of electronic engineer in 1965 and the Ph.D. degree in electronics from the Moscow Radiotekhnika Electronic and Automatic Institute in 1979.

During 1965-1972 he worked in the Kiev Semiconductor Devices Plant in the area of bipolar microwave transistor devices. During 1979-1994 he was working in the Research Institute Saturn as Chief of the Low Noise Microwave GaAs Devices Department. His research interest is in the physics, fabrication technique, and modelling of different GaAs devices. His recent activity include the development of new GaAs MESFET's for power amplifiers.